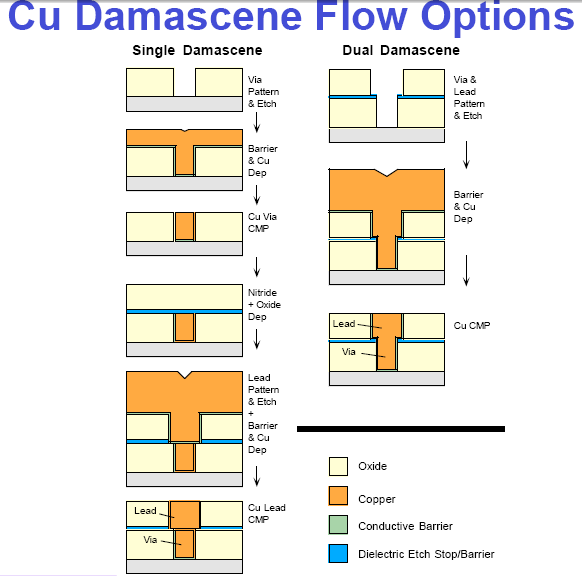

In the dual damascene process, via openings are first anisotropically etched through an inter-metal dielectric (IMD) layer by conventional photolithography and etching.

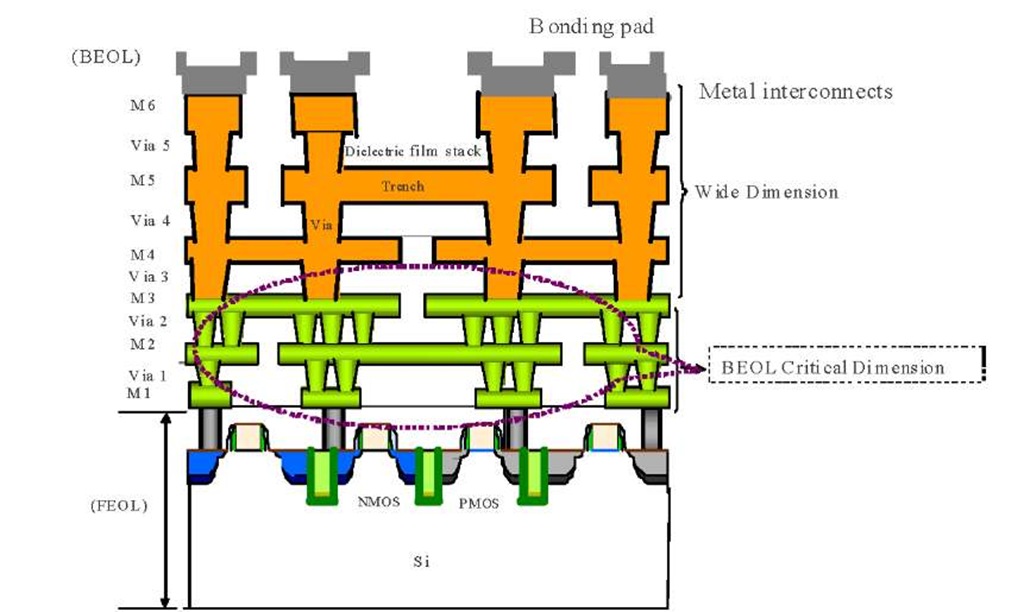

A typical process for forming a multi-layered interconnect structure is a dual damascene process. Accordingly, multiple layers may be required for providing a multi-layered interconnect structure. In the fabrication of semiconductor devices, the size of semiconductor devices has been continuously reduced in order to increase device density. The present invention relates to semiconductor fabrication, and in particular to the fabrication of a semiconductor device by dual damascene process.

0 kommentar(er)

0 kommentar(er)